crosstalk and useful skew

For crosstalk and useful skew, we have to know the basics of setup and hold timing. Here I am going to write here some small concepts related to timing that will be used for crosstalk and useful skew.

Setup time: The minimum time before the active edge of the clock, the input data should be stable i.e. data should not be changed at this time.

Hold time: The minimum time after the active edge of the clock, the input data should be stable i.e. data should not be changed at this time.

Capture edge: the edge of the clock at which data is captured by a captured flip flop

Launch edge: the edge of the clock at which data is launched by a launch flip flop

Launch flip flop: this is a flop from where data is launched.

Captured flip flop: this is the flop on which data is captured.

For setup check

Setup slack check = (required time) min – (arrival time) max

Arrival time = Tlaunch + Tcq+ Tcomb

Required time = Tclk+Tcapture-Tsu

For setup time should not violate the required time should be greater than arrival time.

For hold check

Hold slack check = (arrival time) min – (required time) max

Arrival time = Tlaunch + Tcq + Tcomb

Required time = Tcapture + Thold

For hold time should not violate the arrival time should be greater than the required time.

#AT= arrival time

#RT = required time

Crosstalk noise: noise refers to undesired or unintentional effect between two or more signals that are going to affect the proper functionality of the chip. It is caused by capacitive coupling between neighboring signals on the die. In deep submicron technologies, noise plays an important role in terms of functionality or timing of device due to several reasons.

- Increasing the number of metal layers. For example, 28nm has 7 or 8 metal layers and in 7nm it’s around 15 metal layers.

- Vertically dominant metal aspect ratio it means that in lower technology wire are thin and tall but in higher technology the wire is wide and thin, thus a greater the proportion of the sidewall capacitance which maps into wire to wire capacitance between neighboring wires.

- Higher routing density due to finer geometry means more metal layers are packed in close physical proximity.

- A large number of interacting devices and interconnect.

- Faster waveforms due to higher frequencies. Fast edge rates cause more current spikes as well as greater coupling impact on the neighboring cells.

- Lower supply voltage, because the supply voltage is reduced it leaves a small margin for noise.

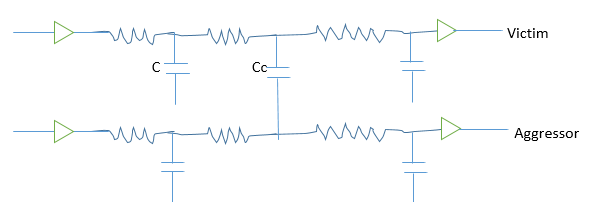

- The switching activity on one net can affect on the coupled signal. The effected signal is called the victim and affecting signals termed as aggressors.

There are two types of noise effect caused by crosstalk

Glitch: when one net is switching and another net is constant then switching signal may cause spikes on the other net because of coupling capacitance (Cc) occur between two nets this is called crosstalk noise.

In fig the positive glitch is induced by crosstalk from rising edge waveform at the aggressor net. The magnitude of glitch depends on various factors.

- Coupling capacitance between aggressor and victim net: greater the coupling capacitance, larger the magnitude of glitch.

- Slew (transition) of the aggressor net: if the transition is more so magnitude of glitch also more. And we know the transition is more because of high output drive strength.

- If Victim net grounded capacitance is small then the magnitude of glitch will be large.

- If Victim net drive strength is small then the magnitude of glitch will be large.

Types of glitches:

- Rise: when a victim net is low (constant 0) and the aggressor net is at a rising edge.

- Fall: when a victim net is high (constant 1) and the aggressor net is at the falling edge.

- Overshoot: when a victim net is high (constant 1)) and the aggressor net is at a rising edge.

- Undershoot: when a victim net is low (constant 0) and the aggressor net is at the falling edge.

Crosstalk delay: when both nets are switching or in transition state then switching signal at the victim signal may have some delay or advancement in the transition due to coupling capacitance (Cc) occur between two nets this is called crosstalk delay.

Crosstalk delay depends on the switching direction of aggressor and victim net because of this either transition is slower or faster of the victim net.

Types of crosstalk:

- Positive crosstalk: the aggressor net has a rising transition at the same time when the victim net has a falling transition. The aggressor net switching in the opposite direction increases the delay for the victim. The positive crosstalk impacts the driving cell, as well as the net, interconnect - the delay for both gets increased because the charge required for the coupling capacitance Cc is more.

- Negative crosstalk: the aggressor net is a rising transition at the same time as the victim net. The aggressor's net switching in the same direction decrease delay of the victim. The positive crosstalk impacts the driving cell, as well as the net, interconnect - the delay for both gets decreased because the charge required for the coupling capacitance Cc is less.

Crosstalk effect on timing analysis:

If the aggressor transition in the same direction as the victim then victim transition becomes fast because of this data will be arrive early means arrival time will be less.

Setup = RT – AT(dec) this is good for setup #dec- decrease

Hold = AT(dec) – RT this is bad for hold

If the aggressor transition in a different direction as a victim then victim transition becomes slow because of this data will be arrive late means arrival time will be more.

Setup = RT – AT(inc) this is not good for setup

Hold = AT(inc) – RT this is good for hold

Consider crosstalk in the clock path:

If the aggressor transition in the same direction as the victim then victim transition becomes fast because of this clock will be arrive early means Required time will be less.

Setup = RT(dec) – AT this is not good for setup

Hold = AT – RT(dec) this is good for hold

If the aggressor transition in a different direction as a victim then victim transition becomes slow because of this clock will be arrive late means the Required time will be more.

Setup = RT(inc) – AT this is good for setup

Hold = AT – RT(inc) this is not good for hold

How to reduce the crosstalk:

- Wire spacing (NDR rules) by doing this we can reduce the coupling capacitance between two nets.

- Increased the drive strength of victim net and decrease the drive strength of aggressor net

- Jumping to higher layers (because higher layers have width is more)

- Insert buffer to split long nets

- Use multiple vias means less resistance then less RC delay

- Shielding: high-frequency noise is coupled to VSS or VDD since shielded layers are connects to either VDD or VSS. The coupling capacitance remains constant with VDD or VSS.

Useful skew:

When clock skew is intentionally add to meet the timing then we called it useful skew.

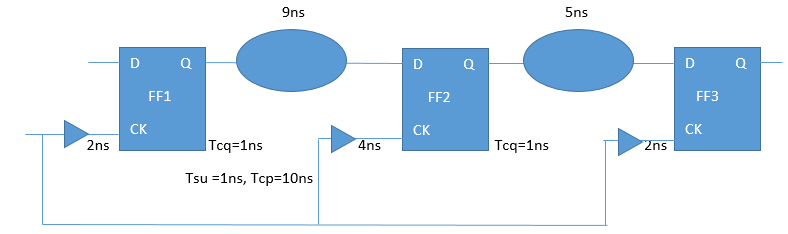

In this fig the path from FF1 to FF2

Arrival time = 2ns + 1ns + 9ns = 12ns

Required time = 10 ns (clock period) + 2ns - 1ns = 11ns

Setup slack = required time – arrival time

= 11ns -12ns

= -1ns (setup violated)

In this fig the path from FF2 to FF3

Arrival time = 2ns + 1ns + 5ns = 8ns

Required time = 10 ns (clock period) + 2ns - 1ns = 11ns

Setup slack = required time – arrival time

= 3ns (setup not violated)

Let’s introduce some clock skew to path ff1 to ff2 to meet the timing. Here we add 2ns extra skew in clock path but we have to make sure about the next path timing violation.

In this fig the path from FF1 to FF2

Arrival time = 2ns + 1ns + 9ns = 12ns

Required time = 10 ns (clock period) + 4ns - 1ns = 13ns

Setup slack = required time – arrival time

= 13ns -12ns

=1ns (setup not violated)

In this fig the path from FF2 to FF3

Arrival time = 4ns + 1ns +5 ns = 10ns

Required time = 10 ns (clock period) + 2ns - 1ns = 11ns

Setup slack = required time – arrival time

= 11ns -10ns

= 1ns (setup not violated)

No comments:

Post a Comment