PHYSICAL ONLY CELLS:

These cells are not present in the design netlist. if the name of a cell is not present in the current design, it will consider as physical only cells. they do not appear on timing paths reports.they are typically invented for finishing the chip.

Tap cells:

- A tap cell is a special nonlogic cell with a well tie, substrate tie, or both.

- Tap cells are placed in the regular intervals in standard cell row and distance between two tap cells given in the design rule manual.

- These cells are typically used when most or all of the standard cells in the library contain no substrate or well taps.

- Generally, the design rules specify the maximum distance allowed between every transistor in a standard cell and a well or substrate tap.

- Before global placement (during the floorplanning stage), you can insert tap cells in the block to form a two-dimensional array structure to ensure that all standard cells placed subsequently comply with the maximum diffusion-to-tap distance limit.

- command in ICC: create_tap_cells, specify the name of the library cell to use for tap cell insertion (‑lib_cell option) and the maximum distance, in microns, between tap cells (‑distance option)

- icc2_shell>create_tap_cells -lib_cell myreflib/mytapcell -distance 30

|

| fig1: TAP Cells and END CAP Cells |

|

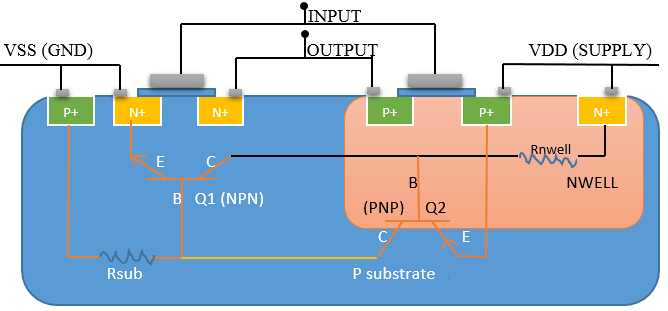

| FIG: latch-up phenomenon |

- when the input and output > VDD: PNP transistor in ON condition: because now P region is more positive than N region in Nwell, therefore Base-Emitter junction of PNP (Q2) transistor is in Forward biased and now this transistor will turn on. Now if we see in the fig the collector of PNP transistor is connected to the base of NPN transistor, because of this connection the current is flowing from collector (PNP) to base (NPN) and then because of this base current the NPN transistor gets turn on and the current flowing from VDD to VSS through these two parasitics transistors. This current is flowing even if we removed the external inputs and outputs and parasitic transistors make a feedback path in which current is latched up and creates a short circuit path.

- when input and output <VSS: NPN transistor in ON condition: Now N region is more negative than P region in P substrate, therefore Base-Emitter junction of NPN (Q1) transistor is in Forward biased and now this transistor will turn on. Now if we see in the fig the Base of NPN transistor is connected to the Collector of PNP transistor, because of this connection the current is flowing from Base (NPN) to Collector (PNP) and then because of this Collector current the PNP transistor gets turn on and current flowing from VDD to VSS through these two parasitics transistors. This current is flowing even if we removed the external inputs and outputs and parasitic transistors make a feedback path in which current is latched up and creates a short circuit path.

In the fig shown above, the value of Rnwell and Rpsub resistance is quite high, if the values of these resistances will reduced then what will happen? The current flowing from the collector of PNP transistor will flow from these resistance paths, i.e current find the low resistance path to reach from VDD to VSS and NPN transistor will never get turn on and in this way, latchup problem will not occur.

Solution for latch-up problem:

Reducing the resistance values: tap the Nwell to VDD and Psubstrate to GND externally.

|

| fig: tapping the VDD with Nwell and VSS with Psub externally |

- These are special-purpose cells whose output is constant high or low. The input needs to be connected to the gate of the transistor and there are only two types of input logic 1 and logic 0, but we do not connect them directly to gate of the transistor as with supply glitches can damage the transistor so we used tie high and tie low cells (these are nothing but resistors to make sure that PG network connected through them ) and output of these cells are connected to the gate of the transistor.

- There will be floating nets because of unused inputs they should be tie with some value either low or high to make them stable.

- Insert the tie cells manually also by command connect_tie_cells, this command insert tie cells and connect them to specified cell ports.

why tie cells are inserted?

The gate oxide is very thin and it is very sensitive to voltage fluctuations. If the Gate oxide is directly connected to the PG network, the gate oxide of the transistor may get damaged due to voltage fluctuations in the power supply. To overcome this problem tie cells are used.

How the circuit looks like and how it will work:

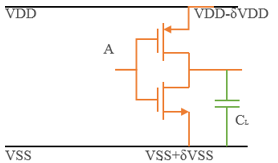

Tie high cells: initially we directly connect VDD to the gate of transistor now we connect the output of these cells to the gate of the transistor if any fluctuations in VDD due to ESD then PMOS circuit pull it back to the stable state. PMOS should be ON always, the input of the PMOS transistor is coming from the output of NMOS transistor and here in NMOS gate and drain are shorted and this is the condition of saturation (NMOS) and NMOS will act as pull-down and always give a low voltage at the gate of PMOS. now PMOS will on and gives stable high output and this output is connected to the gate of transistor

Tie low cells: initially we directly connect VDD to the gate of transistor now we connect the output of these cells to the gate of the transistor, if any fluctuations in VDD due to ESD (electrostatic discharge) then NMOS circuit pull down it back to the constant low stable state.

in fig the gate and drain of PMOS transistor are shorted and hence this is on saturation region and it acts as pull up resistor and it always gives high voltage to the gate of NMOS transistor and because of this high voltage the NMOS transistor will be ON all the time and we get stable low output because it acts as pull-down transistor and this output is connected to the gate of the transistor.

How the circuit looks like and how it will work:

Tie high cells: initially we directly connect VDD to the gate of transistor now we connect the output of these cells to the gate of the transistor if any fluctuations in VDD due to ESD then PMOS circuit pull it back to the stable state. PMOS should be ON always, the input of the PMOS transistor is coming from the output of NMOS transistor and here in NMOS gate and drain are shorted and this is the condition of saturation (NMOS) and NMOS will act as pull-down and always give a low voltage at the gate of PMOS. now PMOS will on and gives stable high output and this output is connected to the gate of transistor

|

| fig: TIE HIGH CELLS |

in fig the gate and drain of PMOS transistor are shorted and hence this is on saturation region and it acts as pull up resistor and it always gives high voltage to the gate of NMOS transistor and because of this high voltage the NMOS transistor will be ON all the time and we get stable low output because it acts as pull-down transistor and this output is connected to the gate of the transistor.

|

| fig: TIE LOW CELLS |

Filler Cells

- To ensure that all power nets are connected, you can fill empty space in the standard-cell rows with filler cells.

- Filler cells have no logical connectivity. these cells are provided continuity in the rows for VDD and VSS nets and it also contains substrate nwell connection to improve substrate biasing.

- Filler cell insertion is often used to add decoupling capacitors to improve the stability of the power supply and discontinuity in power.

- The IC Compiler II tool supports filler cells with and without metal and supports both single-height and multi-height filler cells.

|

| fig2: Filler cells, Decap cells |

why we need continuity for nwell and implantation :

If there is continuity b/w nwell and implant layer it is easier for foundry people to generate them and the creation of a mask is a very costly process so it is better to use only a single mask.

If nwell is discontinuous the DRC rule will tell that place cells further apart i.e maintain the minimum spacing because there is a well proximity effect.

we know nwell is tap to VDD and P substrate is tap to VSS to prevent latchup problem. now if there is a discontinuity in nwell it will not find well tap cells, so we have placed well tap cells explicitly, therefore it will increase the area explicitly, hence we have filler cells so no need to place well tap cells.

when we placed filler cells in the design:

when optimization of clock tree synthesis is completed i.e after timing has been met because let's say if we want to place buffer/inv for optimization purpose we can't place these cells because there is already placed filler cells, and enough area is not there to present buffer/inv, so after timing has been met and routing optimization is done then only placed the filler cells to fill the empty space.

Well proximity effect:

During the manufacturing of chips, we will get these types of problems, that's why they are second-order effects. In this, the transistors that are close to the well edge have different performance than ideally placed transistors, because of this effect the transistor speed can vary by +- 10%.

The transistor placed to the well boundary so it will get many problems during ion implantation. Implanted ion is coming to the well boundary and reflected/scatter from the well boundary to transistors Q1 & Q5 boundary and ions are deposited on the Q1 Q5 boundary. Ion particles are scattered/reflected due to photoresist on both side of nwell wall. these ions are deposited only those transistors who are near to the well boundary, so any one of the terminals of transistors gets affected by ion implantation and the rest of the transistor will get uniform ions.

Decap cells:

If nwell is discontinuous the DRC rule will tell that place cells further apart i.e maintain the minimum spacing because there is a well proximity effect.

we know nwell is tap to VDD and P substrate is tap to VSS to prevent latchup problem. now if there is a discontinuity in nwell it will not find well tap cells, so we have placed well tap cells explicitly, therefore it will increase the area explicitly, hence we have filler cells so no need to place well tap cells.

when we placed filler cells in the design:

when optimization of clock tree synthesis is completed i.e after timing has been met because let's say if we want to place buffer/inv for optimization purpose we can't place these cells because there is already placed filler cells, and enough area is not there to present buffer/inv, so after timing has been met and routing optimization is done then only placed the filler cells to fill the empty space.

Well proximity effect:

During the manufacturing of chips, we will get these types of problems, that's why they are second-order effects. In this, the transistors that are close to the well edge have different performance than ideally placed transistors, because of this effect the transistor speed can vary by +- 10%.

The transistor placed to the well boundary so it will get many problems during ion implantation. Implanted ion is coming to the well boundary and reflected/scatter from the well boundary to transistors Q1 & Q5 boundary and ions are deposited on the Q1 Q5 boundary. Ion particles are scattered/reflected due to photoresist on both side of nwell wall. these ions are deposited only those transistors who are near to the well boundary, so any one of the terminals of transistors gets affected by ion implantation and the rest of the transistor will get uniform ions.

|

| well proximity effect |

- These are typically poly gate transistors where source and drain are connected to the ground rails and the gate is connected to the power rails. (fig2)

- The gate in a transistor consumes most of the power(dynamic) only at the active edge of the clock at which most of the sequential elements are switching.

- No voltage source is perfect hence glitches are produced on the power line due to this huge current drawn from the power grid at the active edge of the clock.

- We already know that power and ground rails are made up of metal and metal have its own resistance and inductance, when current is flowing through these metal wires there is some voltage drop.

- If the power source is far away from a flip flop the chances are that this flop can go into the metastable state due to this IR drop because it will not get sufficient voltage to work properly.

- Decap filler cells are small capacitors which are placed between VDD and GND all over the layout when the logic circuit draw a high amount of current, this capacitor provides extra charge to that circuit. when logic circuit not drawing any current, the de-cap is charged up to maximum capacitance.

we know V= IR + L di/dt.

V= IR (voltage drop due to the metal layer)

V= Ldi/dt (voltage drop due to change in current with respect to time)

now if the voltage drop is greater than Noise margin(NM) of the inverter then it might lead to improper functionality. Let's say NM is 0.4 now 1-0.4=0.6v (anything less than 0.6 will consider as 0 by this inverter)

now let's say voltage drop is 0.5 i.e 1-0.5=0.5v now this will consider as 0 therefore it will lead to improper functionality. now we have seen voltage drop > NM so here de-cap cells comes into picture so these cells are capacitor that holds the reservoir of charges and these cells are placed near to the power-hungry cells, so whenever these cells switch the de-cap cells starts discharging themselves and provided the required voltage to the particular cells and keep the power supply constant to all the elements in the design.

With increasing clock frequency and decreasing supply voltage as technology scales, maintaining the quality of power supply becomes a critical issue. Typically, decoupling capacitors (de-caps) are used to keep the power supply within a certain percentage (e.g., 10%) of the nominal supply voltage. De-caps holds a reservoir of charge and are placed close to the power pads and near any large drivers. When large drivers switch, the de-caps provide instantaneous current to the drivers to reduce IR drop and Ldi/dt effects, and hence keep the supply voltage relatively constant. A standard de-cap is usually made from NMOS transistors in a CMOS process. At the 90nm technology node, the oxide thickness of a transistor is reduced to roughly 2.0nm. The thin oxide causes two new problems: possible electrostatic discharge (ESD) induced oxide breakdown and gate tunneling leakage. Potential ESD oxide breakdown increases the likelihood that an integrated circuit (IC) will be permanently damaged during an ESD event and hence raises a reliability concern. Higher gate tunneling leakage increases the total static power consumption of the chip. As technology scales further down, with a thinner oxide, the result is an even higher ESD risk and more gate leakage. The standard de-cap design experiences these two problems for more please visit the link below.

http://www.ece.ubc.ca/~xmeng/Files/01613147.pdf

Disadvantages of Decap cells:

Boundary cells (End cap cells):

With increasing clock frequency and decreasing supply voltage as technology scales, maintaining the quality of power supply becomes a critical issue. Typically, decoupling capacitors (de-caps) are used to keep the power supply within a certain percentage (e.g., 10%) of the nominal supply voltage. De-caps holds a reservoir of charge and are placed close to the power pads and near any large drivers. When large drivers switch, the de-caps provide instantaneous current to the drivers to reduce IR drop and Ldi/dt effects, and hence keep the supply voltage relatively constant. A standard de-cap is usually made from NMOS transistors in a CMOS process. At the 90nm technology node, the oxide thickness of a transistor is reduced to roughly 2.0nm. The thin oxide causes two new problems: possible electrostatic discharge (ESD) induced oxide breakdown and gate tunneling leakage. Potential ESD oxide breakdown increases the likelihood that an integrated circuit (IC) will be permanently damaged during an ESD event and hence raises a reliability concern. Higher gate tunneling leakage increases the total static power consumption of the chip. As technology scales further down, with a thinner oxide, the result is an even higher ESD risk and more gate leakage. The standard de-cap design experiences these two problems for more please visit the link below.

http://www.ece.ubc.ca/~xmeng/Files/01613147.pdf

Disadvantages of Decap cells:

- These are very leaky.

- The interaction of de-cap cells with package RLC network .since the die is essentially a capacitor with small R, L and package having huge RL network, more de-cap cells placed the more chances of tunning the circuit is into its resonance frequency, since both VDD and GND will be oscillating, many of the designers are fails because of this.

Boundary cells (End cap cells):

- Before placing the standard cells, we can add boundary cells to the block. Boundary cells consist of end-cap cells, which are added to the ends of the cell rows and around the boundaries of objects such as the core area, hard macros, blockages, and voltage areas, and corner cells, which fill the empty space between horizontal and vertical end-cap cells. (fig1)

- End-cap cells are typically nonlogic cells such as a decoupling capacitor for the power rail. Because the tool accepts any standard cell as an end-cap cell, ensure that you specify suitable end-cap cells.

- Boundary cells include both end-cap cells placed on the left, right, top, and bottom boundaries, and inside and outside corner cells and.

- To know the end of the row and at the edges, endcap cells are placed to avoid the cell's damages at the end of the row to avoid the wrong laser wavelength for correct manufacturing.

- Boundary cells protect your design from external signals.

- These cells ensure that gaps do not occur between the well and implant layer and to prevent from the DRC violations.

- When you insert these at the end of the placement row, these will make sure that these cells properly integrated to the design and will have a clean unwell, other DRC clean, hence next block will abut without any issues.

No comments:

Post a Comment