Before 2000 area, delay and performance were the most important parameters, if anyone design circuit the main focus was on how much less area is occupied by the circuit on the chip and what the speed is. Now situation is changed, the performance and speed is a secondary concern. In all nanometer (deep sub-micron) technology power becomes the most important parameter in the design. Almost all portable devices run on battery power. Power consumption is a very big challenge in modern-day VLSI design as technology is going to shrinks Because of

- Increasing transistors count on small chip

- Higher speed of operations

- Greater device leakage currents

Grid structure:

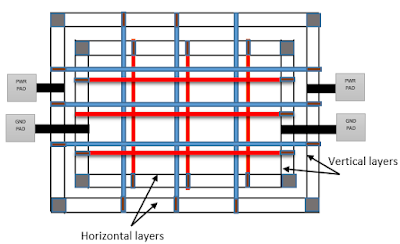

Power planning means to provide power to the every macros, standard cells, and all other cells are present in the design. Power and Ground nets are usually laid out on the metal layers. In this create power and ground structure for both IO pads and core logic. The IO pads power and ground buses are built into the pad itself and will be connected by abutment.

For core logic there is a core ring enclosing the core with one or more sets of power and ground rings. The next consideration is to construct cell power and ground that is internal to core logic these are called power and ground stripes that repeat at regular intervals across the logic or specified region, within the design. Each of these stripes run both vertically and horizontally at regular interval then this is called power mesh.

|

| Ring and core power ground |

The total number of stripes and interval distance is solely dependent on the ASIC core power consumption. As power consumption (static and dynamic) increases the distance of power and ground straps interval increase to reduce overall voltage drop, thereby improving performance.

In addition to the core power and ground ring, macro power and ground rings need to be created using vertical and horizontal metal layers. A macro ring encloses one or more macros, completely or partially with one or more sets of power and ground rings.

It is strongly recommended to check for power and ground connectivity after construction of the entire PG network.

Standard cell are placed in a row since they are placing side by side they are touching each other, and horizontal routing across the cells already done so you don’t have to anything it’s like a continuous line. That’s why we are placing filler cells if any gap is thereafter optimization.

|

| standard cells are placed in the rows |

Power planning involves

- Calculating number of power pins required

- Number of rings, stripes

- Width of rings and stripes

- IR drop

The calculation depends on the power consumed by chip, total current drawn, current rating of power pad (A/m), current rating of metal layers, and the percentage of current flowing through metal layers.

Inputs of power planning

- Netlist(.v)

- SDC

- physical and logical libraries (.lef & .lib)

- TLU+

- UPF

Level of power distribution

- Rings: carries VDD and VSS around the chip

- Stripes: carries VDD and VSS from the ring

- Rails: connect VDD and VSS to the standard cell’s VDD and VSS

POWER PLANNING MANAGEMENT

Core cell power management:

- In this power rings are formed around the core.

- If any macros/IP is power critical than create separate power ring for particular macro/IP.

- Number of power straps are created based on the power requirement.

I/O cell power management:

In this power rings are formed for I/O cells and trunks are created between core and power rings and power pads.

Ideal power distribution network has the following properties:

- Maintain a stable voltage with little noise

- Avoids wear out from EM and self-heating

- Consume little chip area and wiring

- Easy to layout

Real networks must balance these competing demands, meeting targets of noise and reliability. The noise goal is typically ±10%; for example, a system with a nominal voltage Vdd= 1.0 V may guarantee the actual supply remains within 0.9-1.1V. The two fundamental sources of power supply noise are IR drop and L di/dt noise.

IR Drop:

The power supply in the chip is distributed uniformly through metal layers across the design and these metal layers have their finite amount of resistance. When we applied the voltage the current starts flowing through these metal layers and some voltage is dropped due to that resistance of a metal wire and current. This drop is called IR drop. Because of IR drop, delay will increase and it violates the timing. And this will increase noise and performance will be degraded.

The value of an acceptable IR drop will be decided at the start of the project and it is one of the factors used to determine the derate value. If the value of the IR drop is more than the acceptable value, it calls to change the derate value. Without this change, the timing calculation becomes optimistic.

For example, a design needs to operate at 1.2 volts and it has tolerance (acceptable IR drop limit) of ±0.4 volts, so we ensure that the voltage across VDD and VSS should not fall below 0.8v and should not rise above 1.6v. If the drop will be in this limit it does not affect timing and functionality

Power routes generally conduct a lot of current and due to this IR drop will become into the picture so we are going to higher layers to make these routes less resistive. For power routing top metal layers are preferred because they are thicker and offer less resistance.

For example, if there are 15 metal layers in the project then top two or three layers used by hierarchy people(top level or full chip) and metal 11 and metal 12 used for power planning purposes.

There are two types of IR drop

- Static IR drop

- Dynamic IR drop

Static IR drop:

This drop is independent of cell switching. And this is calculated with the help of metal own resistance.

Methods to improve static IR drop

- We can go for higher layers if available

- Increase the width of the straps.

- Increase the number of wires.

- Check if any via is missing then add more via.

Dynamic IR drop:

This drop is calculated with the help of the switching of cells. When a cell is switching at the active edge of the clock the cell requires large current or voltage to turn on but due to voltage drop sufficient amount of voltage is not reached to the particular cell and cell may be goes into metastable state and affect the timing and performance.

Methods to improve dynamic IR drop

- Use de-cap cells.

- Increase the number of straps.

Tools used for IR drop analysis:

- Redhawk from Apache

- Voltage storm from cadence

Electromigration:

When a high density of current is flowing through metal layers, the atoms (electron) in the metal layers are displaced from their original position causing open and shorts in the metal layers. Heating also accelerates EM because higher temperature cause a high number of metal ions to diffuse.

In higher technology nodes we saw the EM on power and clock metal layers but now in lower nodes the signal metal layers are also needed to be analyzes due to an increased amount of current density.

Clock nets are more prone to EM because they have high switching activity, because of this only we are avoiding to use high drive strength clock buffers to build the clock tree.

Methods to solve EM:

- Increase the width of wire

- Buffer insertion

- Downsize the driver

- Switch the net to higher metal layers.

- Adding more vias

- Keep the wire length short

Checklist after power planning:

- All power/Ground supplies defined properly?

- Is IR drop acceptable?

- Is the power supply is uniform?

- Are specials cell added? (Tap cells and end cap cells)

- Any power related shorts/opens in the design?

No comments:

Post a Comment